-

Chiplet:延续摩尔定律——先进制程替代之光!

价值投机小学生

/ 2022-08-09 12:12 发布

/ 2022-08-09 12:12 发布作者

: 蒋高振, : 浙商证券设计IP公司

: ; 封装载板

: 。 1.

Chiplet

: ! 1.1.Chiplet助力先进制程弯道超车

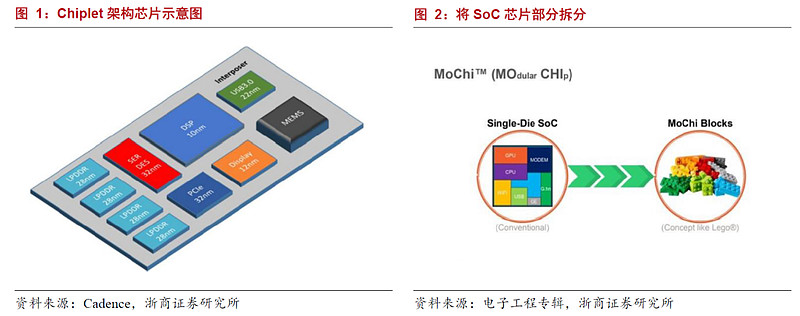

Chiplet(芯粒)模式是在摩尔定律趋缓下的半导体工艺发展方向之一

。 近几十年来

, , , 。 、 、 , , 。 后摩尔定律时代的主流晶片架构SoC (系统单晶片)推动摩尔定律继续向前发展

, , , 。 Chiplet模式或存在弯道超车机会

, , , , , 、 。 , ( 、 ) 、 、 。 Chiplet方案对封装工艺提出了更高的要求

。 , , , , , 、 、 。 , 。

国际巨头成立UCIe产业联盟促进互联协议标准

。 , 。 , , , 。 英特尔

、 、 、 、 、 、 、 、 、 , , 。 , , 。 1.2. 灵活性+低成本催生Chiplet需求

与传统的SoC方案相比

, 、 、 , 。 Chiplet模式可以自由选择不同分区的工艺节点

。 , 。 、 、 、 , 、 , 。 , , , 。 Chiplet模式有利于提高良率

, 。 , , , 。 , , , 。 Chiplet模式可以实现产品重复使用

, 。 , , 。 , , 。 Chiplet模式目前还暂时存在对先进封装技术要求高

、 。 、 ; 要保证各裸芯片之间的数据实现高速、 ; 相对先进制程Chiplet模式散热能力较差, 。 2.

巨头布局

: ! 2.1. 华为

: 华为推出基于Chiplet技术的7nm鲲鹏920处理器

。 , , , , 、 、 , 。 , , 。 , 。 。 , , 。

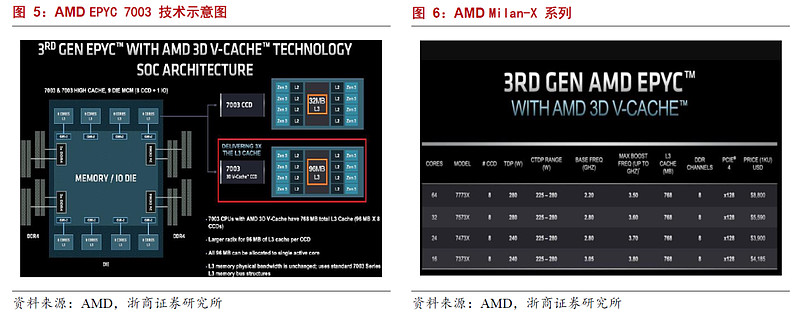

2.2. AMD

: AMD联手台积电推出3D Chiplet产品

。 , , 。 , , 。 , 。

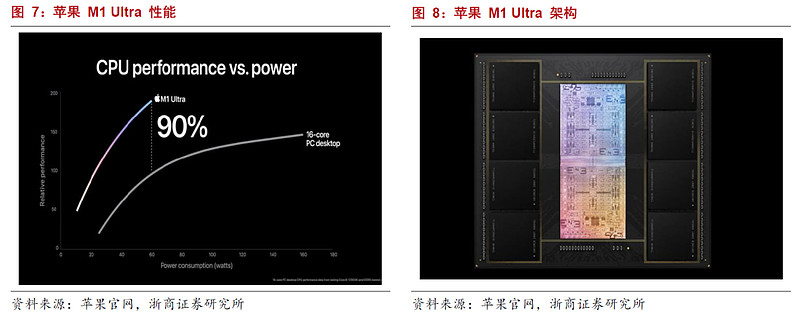

2.3. 苹果

: 苹果推出采用台积电CoWos-S桥接工艺的M1 Ultra芯片

, 。 , , , 。 , , 。 , ( ) , , 。 , 。

3.

产业革新

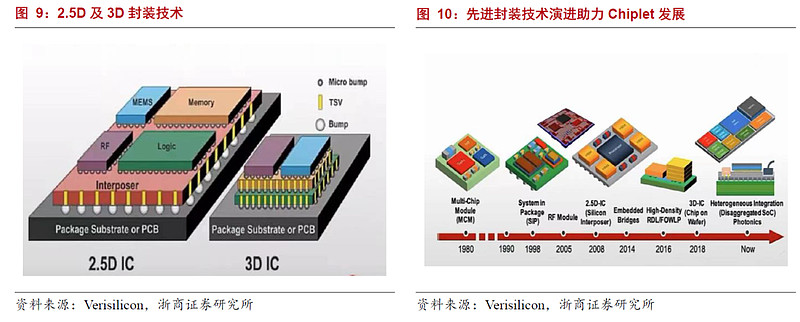

: ! 3.1. 先进封装提升设计弹性

Chiplet目前封装方案主要包括2.5D封装

、 、 。 ( ) , ( ) , , ( ) ( ) , , 。 , , ( ) , 。 , 。

国际厂商积极布局Chiplet封装

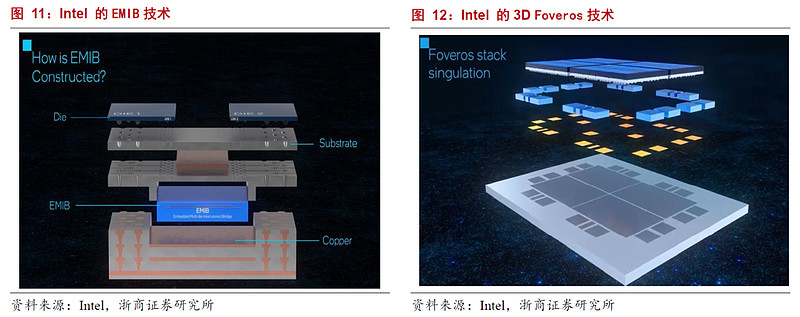

。 、 、 , 。 Intel推出3D堆叠异构系统集成技术Foveros与嵌入式多芯片互联桥接技术EMIB

。 , , 。 , 、 , 。 , , , 。

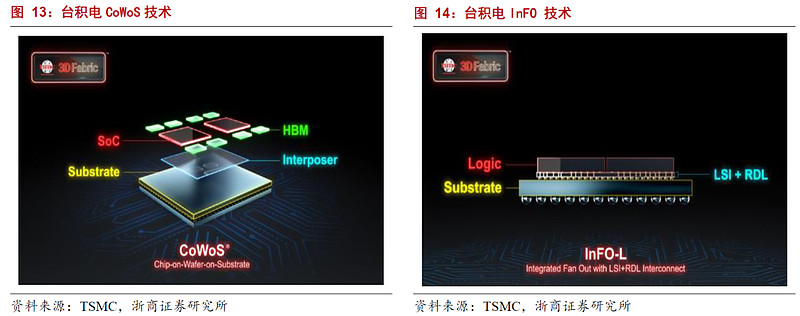

TSMC推出的3D Fabric

, 、 。 , , ( ) ( ) , , 、 、 。 , , 。 。

国内企业通富微电

、 。 , , , , , , , 。 , , 、 、 、 、 、 , 。 Chiplet封装推动对芯片测试机的需求增长

。 , , , , 。 、 , 。 3.2. IP复用提高设计经济性

Chiplet的发展有利于实现

“ IP芯片化” 。 , , 。 , 。 , , 。

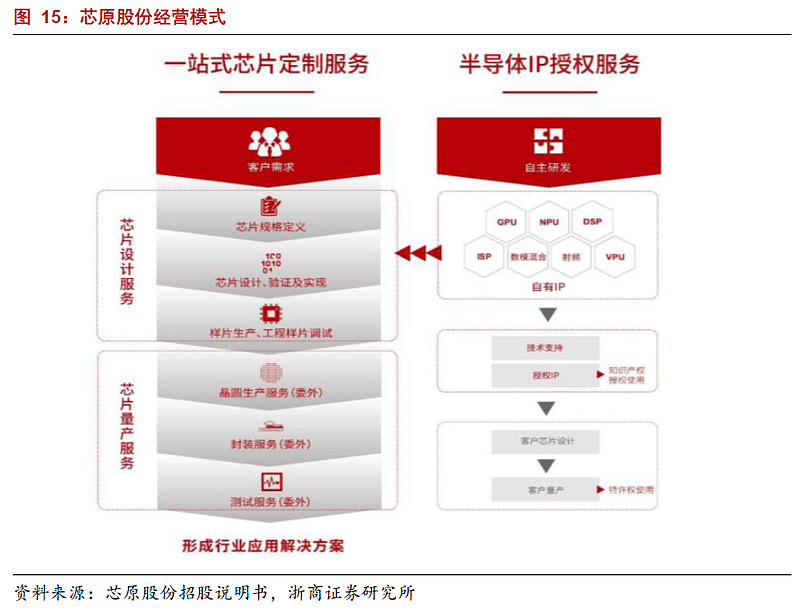

芯原股份作为国内最大的半导体IP供应商有望受益Chiplet发展

。 、 , , , 。 “ IP芯片化” 和“ 芯片平台化” 来实现Chiplet产业化, 、 , 。 , , 、 、 , 。 4.

受益标的

: ! 先进封装

: , 。 , 。 , 、 。 IP公司

: , 。 , , 。 封测设备

: Chiplet方案的落地的关键便在于先进封装技术的实现, 。 , 。 , 、 、 、 。 封装载板

: 、 、 , 、 , 。 、 ,

水晶球APP

高手云集的股票社区

X

公安备案号 51010802001128号

公安备案号 51010802001128号