-

中芯国际静悄悄的先进封装:AMD较劲英特尔,三星再现黑科技

老范说评 / 2021-06-15 17:27 发布

如果用一个字来形容先进封装市场,那就是一个字:乱!

在先进封装市场,除了日月光、安靠等传统的OSAT厂商和英特尔、三星等IDM厂商,就连台积电这样的Foundry也耐不住寂寞,纷纷下海了。

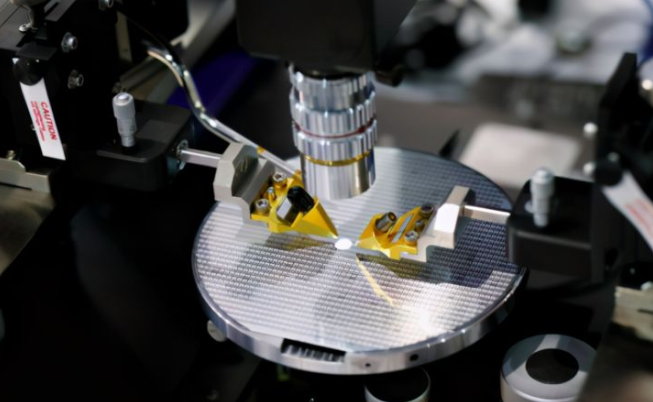

尝鲜上瘾了—说说AMD的先进封装技术

在上个月底的COMPUTEX TAIPEI Virtual上,AMD CEO苏大妈(Lisa Su)介绍了AMD的最新产品和技术,其中便提到了AMD的先进封装—即基于3D Chiplet技术的3D V-Cache技术。该技术使用台积电的3D Fabric先进封装技术,成功将包含有64MB L3 Cache的Chiplet以3D堆叠形式与处理器封装在一起。

AMD本身在封装领域有多年积累的,转向Fabless后,公司于2015年开始使用HBM技术发布了Fury X显卡,通过堆叠将单个Die的容量达到8GB,位宽达到1024位。2017年公司采用MCM多芯片模块技术发布了Zen架构的锐龙CPU,使得多核扩展变得更加有效,也避免了大核心带来的良率问题。2019年推出了使用Chiplet技术的Zen2架构,通过将CPU Die与I/O Die进行分离,将CPU Die做得更小,扩展更多核心也变得更加容易。再到上月底AMD推出3D Chiplet产品锐龙5000,可以说近几年在AMD对英特尔摩擦的路上,先进封装技术起到重要的作用。

资料来源:AMD的2.5D HBM技术与先进封装技术产品,公开资料整理,阿尔法经济研究

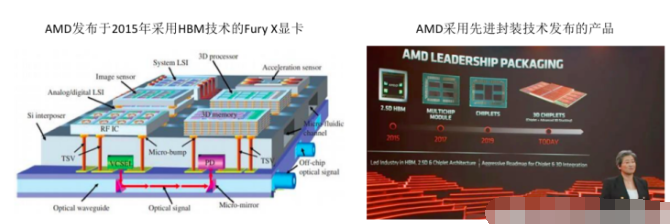

先进封装技术有两条技术路径:第一条是采用Chiplet,即在封装系统里该用数量更多但尺寸更小的芯片粒作为基本单元,在提升良率的同时还可以实现更灵活的异构集成,因为不同的芯片粒可以采用不同的技术节点。第二条是采用2.5D/3D先进封装技术,提高芯片互联密度,解决芯片之间的通信带宽。AMD采用的HBM和英特尔推出的EMIB嵌入式多核心互连桥接封装技术就是典型的2.5D技术:

资料来源:英特尔EMIB封装技术,公开资料整理,阿尔法经济研究

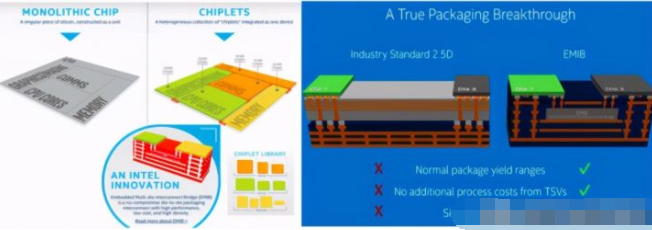

英特尔的3D封装技术是Foveros,其允许芯片面对面堆叠,通过使用TSV工艺在有源转接板上集成不同类型的器件,实现不同工艺、结构和用途的芯片的整合。比如英特尔Core i5-L16G7中将运算芯片与海力士LPDDR4 DRAM集成在PoP架构中,采用Foveros的面对面堆叠和Via-Middle TSV工艺将10nm芯片与22nm转接板直接互连:

资料来源:英特尔Foveros封装技术,公开资料整理,阿尔法经济研究

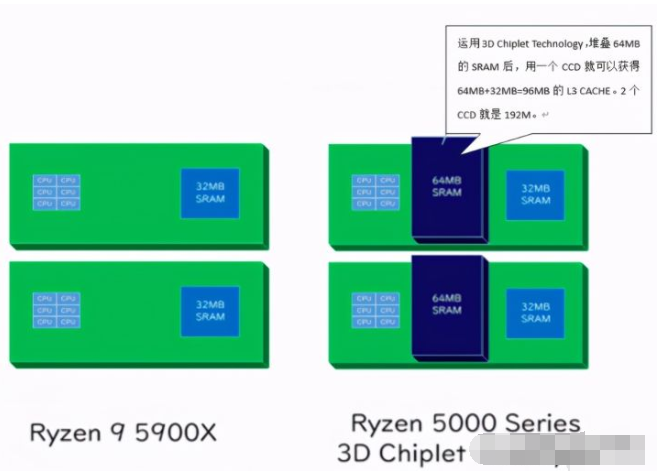

AMD的3D Chiplet则是把2.5D/3D和Chiplet技术相融合,处理器和堆叠的L3 Cache使用了Chiplet,3D V-Cache和处理器Chiplet之间使用了高密度互连,其互连密度相比2D Chiplet提高200多倍,相比传统3D IC技术提高了15倍。

在此次发布会上AMD的锐龙5000在CCD芯片上堆叠了7nm工艺制造的SRAM,将64M的SRAM堆叠在CPU核上,SRAM两边用硅填充。芯片和芯片之间采用TSV技术,穿透CPU芯片上的通孔后与CPU的中介层直接连接,因此也省去了基板,CPU和SRAM之间可以高速通信:

资料来源:AMD采用3D封装技术的锐龙5000与锐龙9 5900X区别,公开资料整理,阿尔法经济研究

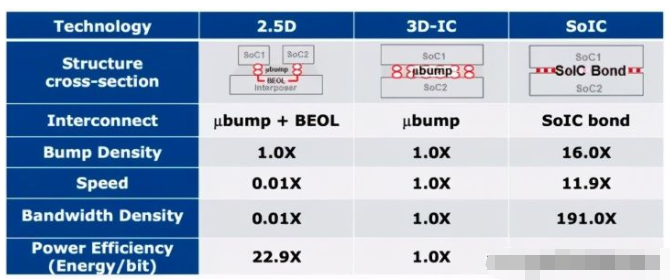

当然AMD能推出先进封装产品还是要靠台积电,其通过优化和整合而成的3D Fabric先进封装技术相比传统基于Bump的3D IC技术,互连密度提升了16倍:

资料来源:三种封装技术性能对比,公开资料整理,阿尔法经济研究

三星先进封装浮出水面,中芯国际静悄悄

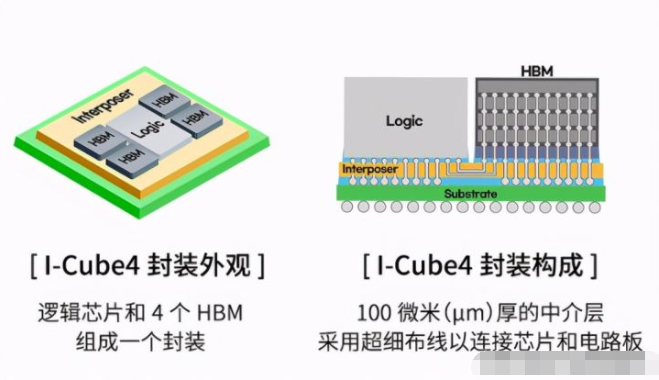

今年5月三星宣布其2.5D封装技术Interposer-Cube4(I-Cube4)完成开发。三星的I-Cube4同样是一种异构集成技术,可以将一个或多个逻辑芯片或HBM通过中介层集成在一个芯片里,有望应用于HPC、AI、5G和数据中心等领域:

资料来源:三星I-Cube4封装技术,公开资料整理,阿尔法经济研究

可以清楚地看到,三星的I-Cube4封装技术中通过TSV技术将堆叠在中介层上面的逻辑IC或HBM与下层的衬底相连接。但由于I-Cube4中中介层厚度约为100微米,因此较大的中介层容易出现弯曲或翘曲,影响产品良率。

按照三星的技术规划,更复杂的I-Cube6技术将可同时封装6颗HBM,而I-Cube4中堆叠了4个HBM,显然I-Cube6将更为复杂。

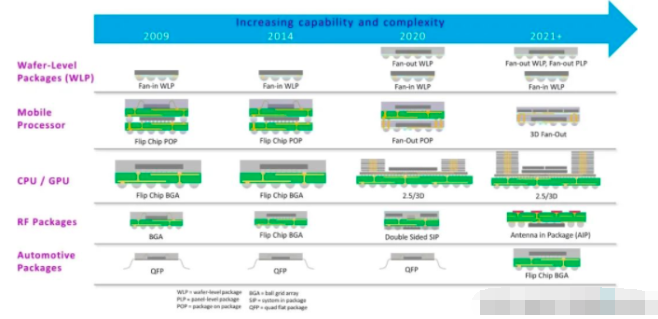

正如业内所言,目前先进封装技术进入新的阶段。除了台积电等进入先进封装,包括OSAT厂商在内,各家推出了种类繁多的封装技术,比如大热的2.5/3D和Chiplet,还有SiP、FC、Fan-Out等,为客户提供更多的技术选项:

资料来源:先进封装技术发展路径,公开资料整理,阿尔法经济研究

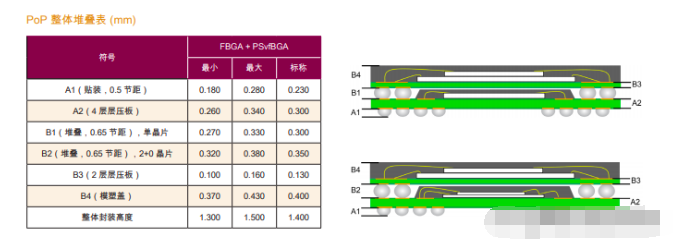

安靠是全球第二大封测厂商,也是美国唯一进入全球前十的封测厂商。安靠在PoP技术上具有深厚的积累,早在2004年便发布了广受欢迎的超细节距BGA可堆叠封装平台,可提供焊盘节距最小可达45微米单列、厚度75-125微米的多种PoP封装服务:

资料来源:安靠PoP封装技术,公司官网整理,阿尔法经济研究

国内三大封测厂商中,华天科技开发的eSIFO扇出型晶圆级封装技术采用硅基技术和150微米的超薄封装,适用于最多5个不同工艺、不同尺寸及不同功能芯片的封装。其3D封装技术是3D eSinC,可以集成多个不同尺寸和不同功能的芯片。5月底公司拟定增51亿元用于多芯片封装、高密度系统级封装和TSV及FC封装:

资料来源:华天科技3D eSinC封装技术,会议资料整理,阿尔法经济研究

长电科技现已具备可与日月光相抗衡的SiP,并拥有自主知识产权的Fan-outeWLB、WLCSP、SiP、Bumping、FC-BGA等多项封装技术。

蒋尚义入主中芯国际后将负责公司先进封装尤其是Chiplet封装技术,该技术目前火热,而且台积电、英特尔等已经相继推出了小芯片产品或技术。但是目前中芯国际在先进封装上还是静悄悄。

另外值得关注的是,在先进封装中EDA厂商将扮演很重要的角色。比如Mentor Graphics推出的HDAP解决方案能对多芯片封装进行快速的原型设计、规划、设计和验证,协助客户构建完整的先进封装技术。

但是正如芯和半导体CEO凌峰所言,不同芯片之间、芯片与封装之间,EDA在设计与分析上都存在一道"墙",如何打破芯片与封装之间的"墙",如何实现EDA平台数据一致性,完成信号、电源、热等协同设计,如何在统一的数据库完成仿真分析,将成为SiP封装技术进一步发展的重要推动力。

这一论断也适用于其他先进封装技术,而目前EDA仍然是国产半导体产业的重大短板之一。

:

水晶球APP

高手云集的股票社区

X

公安备案号 51010802001128号

公安备案号 51010802001128号